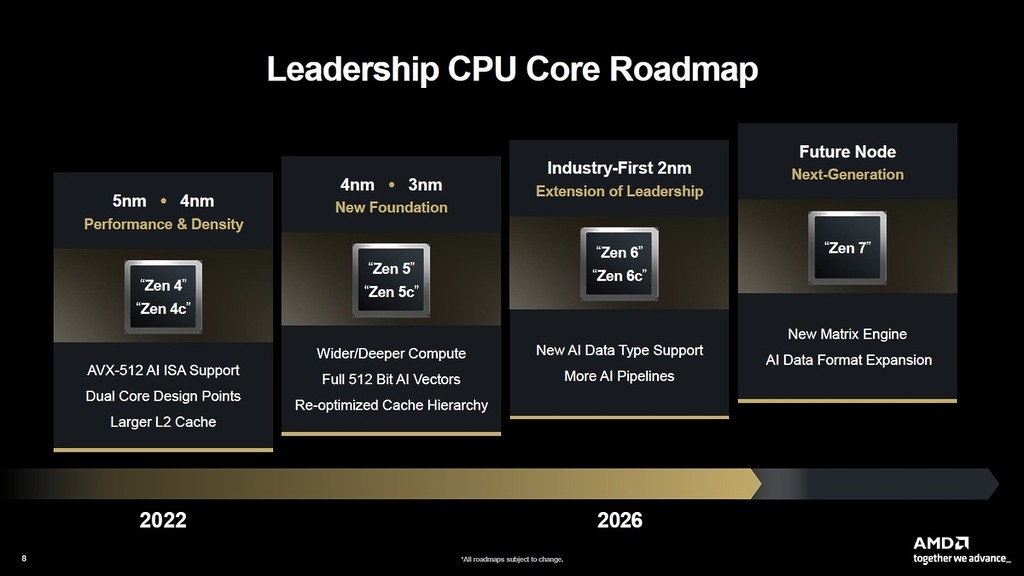

AMD 於上月剛確認下代 Zen 6 架構,將成為業界首款採用台積電 2nm 製程生產的處理器,但詳細技術資料仍然只聞樓梯響。不過近日 AMD 在官網公開一份名為《Performance Monitor Counters for AMD Family 1Ah Model 50h-57h Processors》的技術文件,以及有更新的 GCC 16 Complier,揭示了 Zen 6 並非以往 Zen 4 及 Zen 5 的簡單進化版本,而是在架構上有更大改變,有意設計為更寬廣、更重視吞吐量設計的處理器。

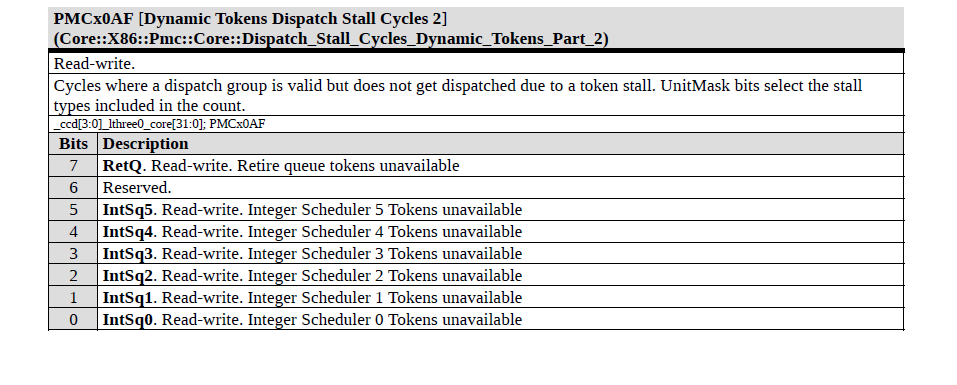

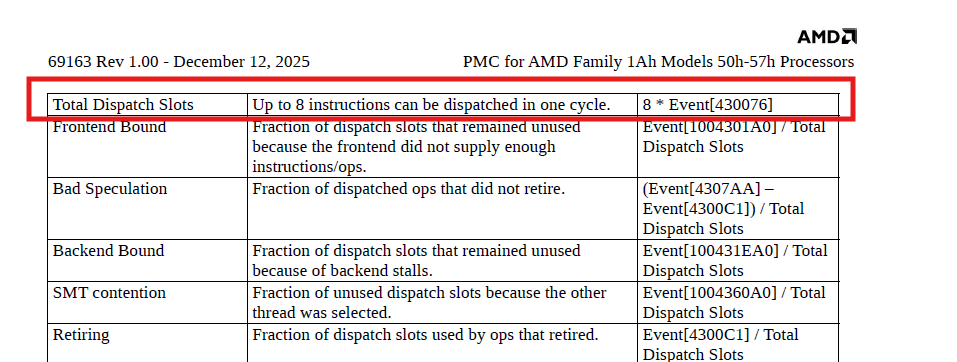

文件透露,AMD 將 Zen 5 的單一統一排程器改為 Zen 6 的六個獨立排程器(Integer Schedulers)。雖然 AMD 未在文件中解釋此變更的原因,但業界普遍預期這種設計能讓每個排程器更精細簡潔,減少電路複雜度和內部延遲,從而降低功耗並有助達成更高時脈。同時,文件透過多處描述(如 SMT contention 和 thread 資源分配),暗示 Zen 6 支持多執行緒(SMT)模式,這些改進結合起來,預計能優化資源分配和並行運算效能。另一方面,文件顯示 Zen 6 擴展至 8-wide dispatch engine,讓更多指令能同時進入執行階段,比 Zen 5 的 6-wide 設計更寬廣。這有助處理向量密集任務,例如 AVX-512 指令,從而提升整體並行性和吞吐量。

除了這份技術文件,外媒還發現 AMD 更新了 GCC 16(GNU Compiler Collection),新增「znver6」支援,加入 AVX512_BMM、AVX512_FP16、AVX_NE_CONVERT、AVX_IFMA 和 AVX_VNNI_INT8 等新 ISA 特性。這與文件中提到的 FP64、FP32、FP16 和 BF16 資料格式相呼應。這意味 Zen 6 可執行「full-width」AVX-512 指令,並確認支持 FP16,包括 FMA/MAC 運算以及混合浮點-整數向量執行(涵蓋 VNNI 類、AES 和 SHA 運算)。由於 AI 模型常混合 BF16(用於訓練)和 FP16 (用於推理),Zen 6 的完整支援和快速轉換功能,能有效減少額外運算量,進一步加速 AI 表現,尤其適合非完整 512-bit 向量運算的情境。

現時業界預期 AMD 或將於 2026 年尾推出 Zen 6 架構處理器,包括伺服器 EPYC 處理器的 Venice 系列、桌上型 Ryzen 處理器的 Olympic Ridge 系列,以及流動版 Ryzen 的 Medusa Point 系列。當中 Venice 系列可能高達 256 核心;流動版 Ryzen 的 Medusa Point 則可能具備高達 24 核心,並由 2 個 12 核心的 CCX/CCD chiplet 組成,每個 CCX/CCD 的 L3 Cache 或將由 32 MB 增至 48 MB。早前更有消息指,AMD 有意將新 Zen 6 架構處理器時脈推上 7GHz 大關。若 Zen 6 真的大改核心設計、核心數量大增兼具更高時脈,它能否成為半導體界有力的 「Game Changer」?相信大家都會十分期待,但還待明年才有分曉。

來源:AMD、Overclock 3D、Tom’s hardware、Phoronix